# Designer's Guide

January 1986

High-speed CMOS

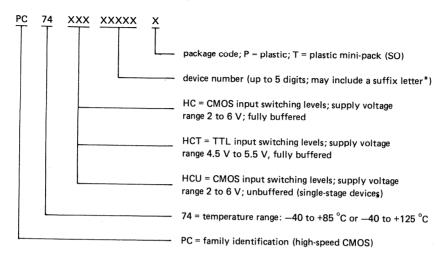

#### **ORDERING INFORMATION**

#### TYPE NUMBER DESIGNATIONS

\* Example suffix "B": this type has bus driver output capability in contrast with the plane version.

#### **DESIGNER'S GUIDE**

|                                                    |                                       | page |

|----------------------------------------------------|---------------------------------------|------|

| Introduction                                       | · · · · · · · · · · · · · · · · · · · | 3    |

| HCMOS family characteristics                       |                                       | 7    |

| Family specifications                              |                                       |      |

| Data sheet specification guide                     |                                       | 19   |

| Definitions of symbols                             |                                       | 21   |

|                                                    |                                       |      |

| User guide                                         |                                       | 23   |

| Application notes                                  |                                       | 59   |

| Interfacing and protection of circuit board inputs |                                       | 61   |

| Standardizing latch-up immunity tests              |                                       | 65   |

| Power dissipation                                  |                                       |      |

| Power supply decoupling                            |                                       | 85   |

| Battery back-up                                    |                                       |      |

| Protection in the automotive environment           |                                       | 97   |

| Astable multivibrators                             |                                       |      |

| Crystal oscillators                                |                                       |      |

| Schmitt trigger applications                       |                                       |      |

| Using 74HCT HCMOS to replace LSTTL and drive tra-  | nsmission lines .                     | 125  |

| Modifying LSTTL test programs to test HCMOS logic  | ICs                                   | 139  |

| Handling precautions                               |                                       |      |

|                                                    |                                       |      |

| Quality - HCMOS logic ICs                          |                                       | 151  |

|                                                    |                                       |      |

| Selection guide                                    | · · · · · · · · · · · · · · · · · · · | 161  |

| Functional index                                   |                                       |      |

| Numerical index                                    |                                       |      |

| Cross-reference guide: TTL to HCMOS                |                                       |      |

| Cross-reference guide: CMOS to HCMOS               |                                       | 181  |

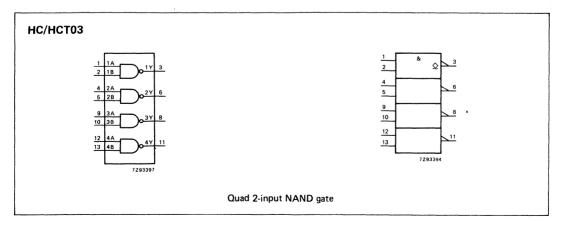

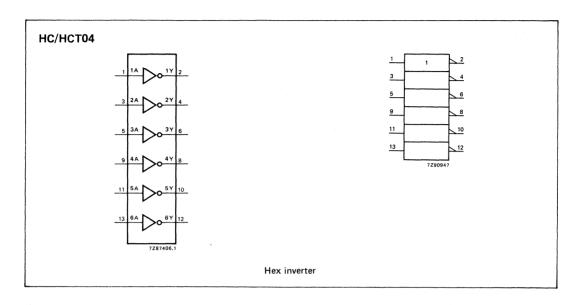

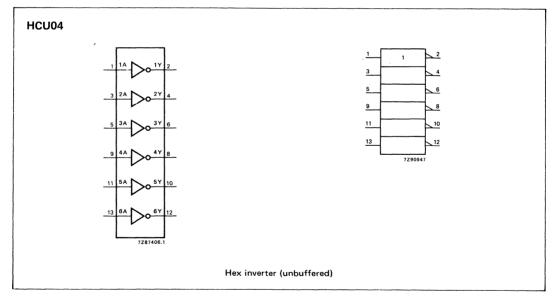

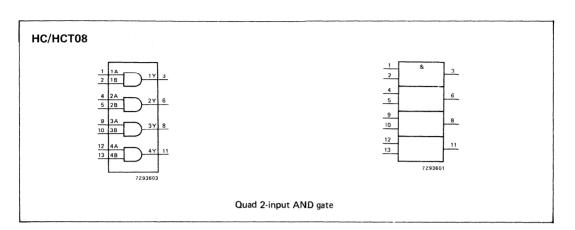

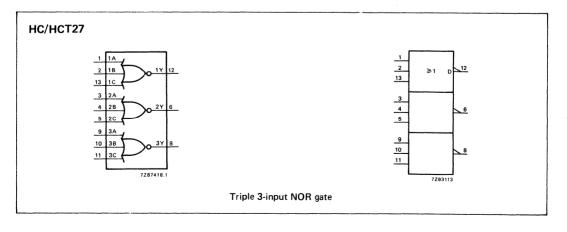

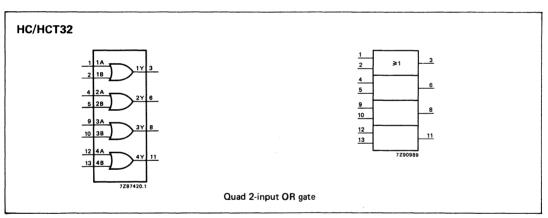

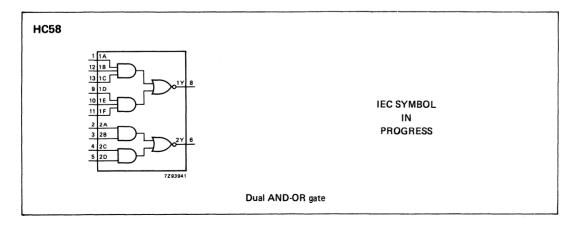

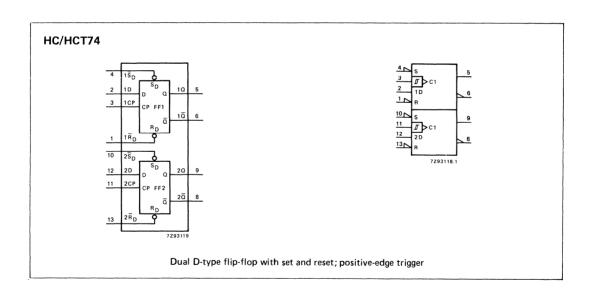

| Functional diagrams; IEC logic symbols             | ,                                     | 185  |

| IEC symbology                                      |                                       | 239  |

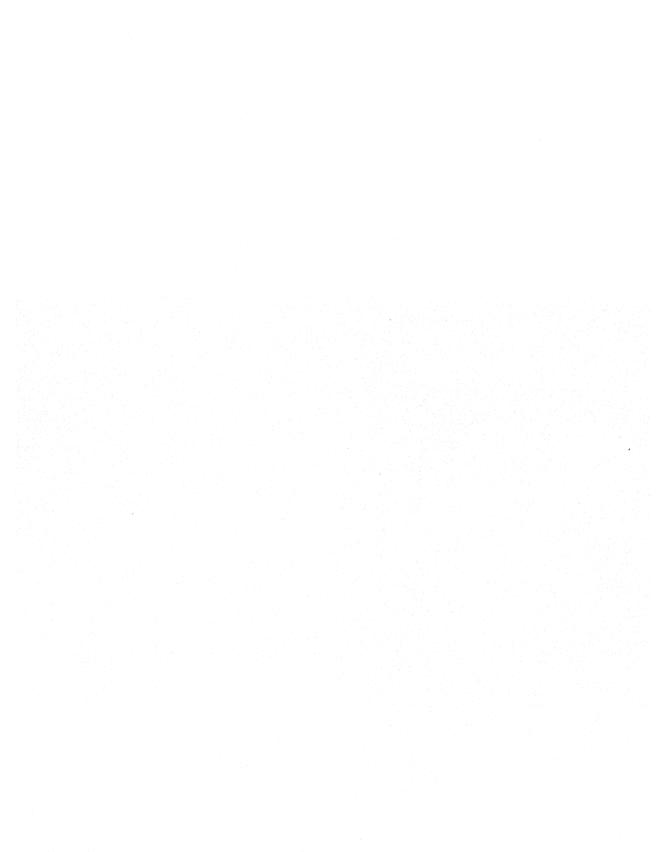

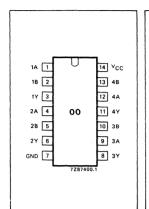

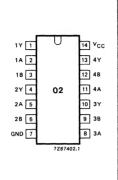

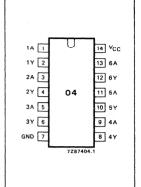

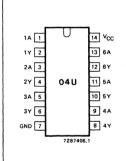

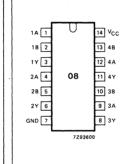

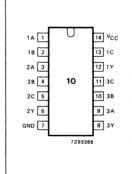

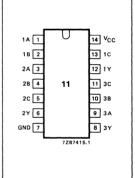

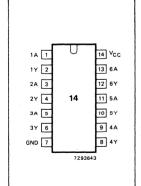

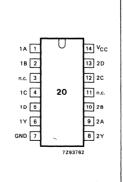

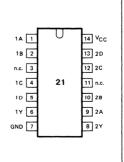

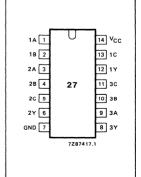

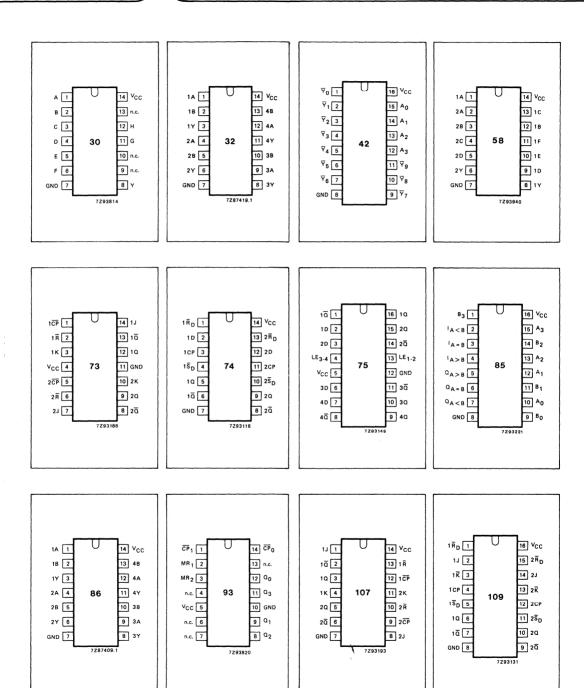

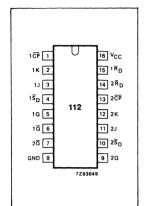

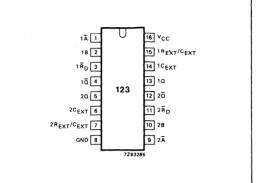

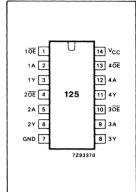

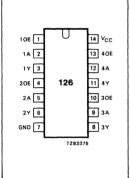

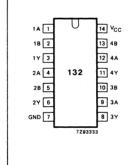

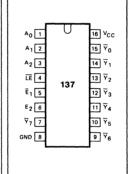

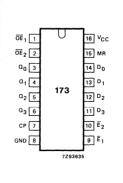

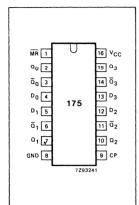

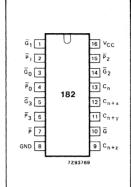

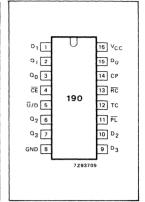

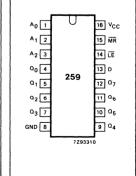

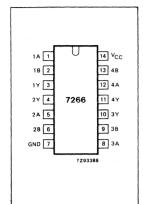

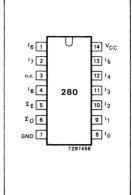

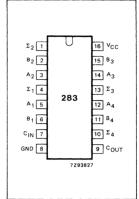

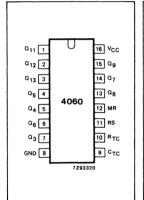

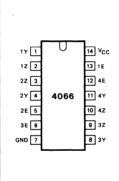

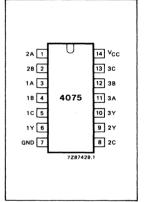

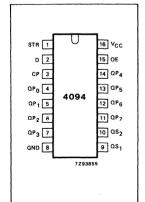

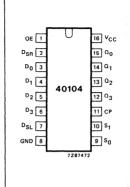

| Pin configurations                                 |                                       | 263  |

## INTRODUCTION FOR THE HCMOS DESIGNER'S GUIDE

This guide has been prepared to provide an understanding of the principles involved in the design of systems using our 74HC/HCT/HCU family of high-speed CMOS (HCMOS) logic ICs. Design examples and performance are given for a wide variety of HCMOS applications, together with methods of protecting HCMOS when it is used in the automotive environment. General circuit board construction principles are also given, covering subjects such as power supply decoupling, interfacing and protection of circuit board inputs. The guide also covers important subjects such as handling, quality, and using HCMOS to replace LSTTL to reduce power consumption without loss of speed. The HCMOS family specification, comprehensive lists of available logic functions and an explanation of the new IEC logic symbols are also included.

The wealth of information contained within this guide is primarily intended for the use of logic circuit and system designers but will also be invaluable to technicians, students and others interested in obtaining a deeper understanding of HCMOS ICs so they can fully exploit their outstanding performance.

### HCMOS FAMILY CHARACTERISTICS

|                                  |   |   |   |   |   |   |  |   |   |   |   |   | p | age |

|----------------------------------|---|---|---|---|---|---|--|---|---|---|---|---|---|-----|

| Family specifications            |   | • | • | • | • |   |  | • | • | • | • | • | • | 9   |

| Data sheet specification guide . | • |   |   |   | • | • |  |   |   | • |   |   |   | 19  |

| Definitions of symbols           |   |   |   |   |   |   |  |   |   |   |   |   |   | 21  |

#### **GENERAL**

These family specifications cover the common electrical ratings and characteristics of the entire HCMOS 74HC/HCT/HCU family, unless otherwise specified in the individual device data sheet.

#### INTRODUCTION

The 74HC/HCT/HCU high-speed Si-gate CMOS logic family combines the low power advantages of the HE4000B family with the high speed and drive capability of the low power Schottky TTL (LSTTL).

The family will have the same pin-out as the 74 series and provide the same circuit functions.

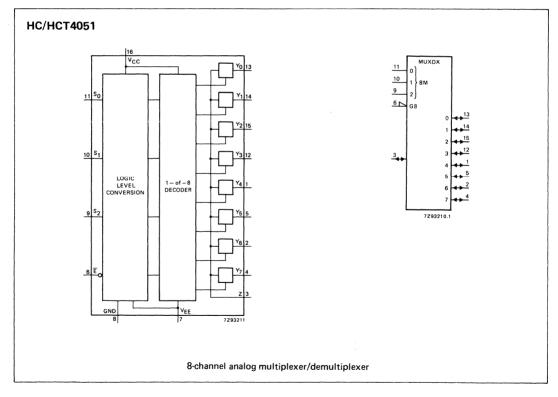

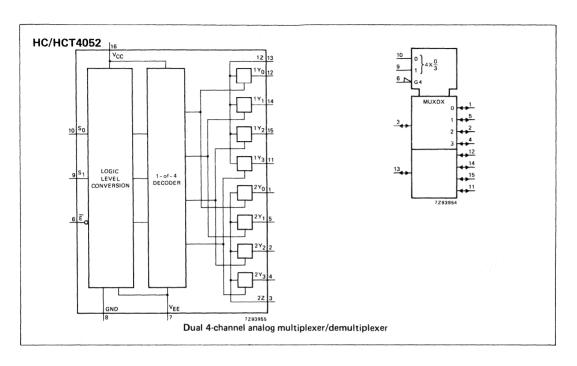

In these families are included several HE4000B family circuits which do not have TTL counterparts, and some special circuits.

The basic family of buffered devices, designated as XX74HCXXXXX, will operate at CMOS input logic levels for high noise immunity, negligible typical quiescent supply and input current. It is operated from a power supply of 2 to 6 V.

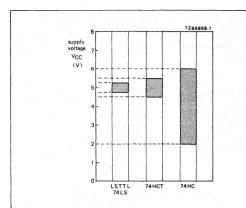

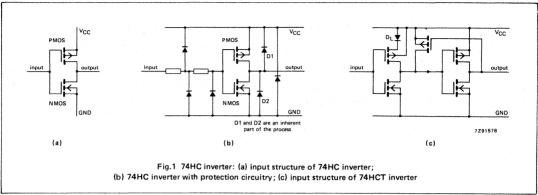

A subset of the family, designated as XX74HCTXXXXX, with the same features and functions as the "HC-types", will operate at standard TTL power supply voltage (5 V ± 10%) and logic input levels (0.8 to 2.0 V) for use as pin-to-pin compatible CMOS replacements to reduce power consumption without loss of speed. These types are also suitable for converted switching from TTL to CMOS.

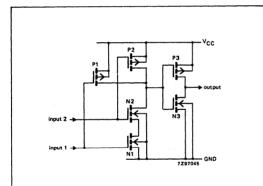

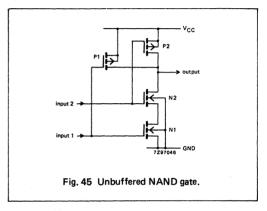

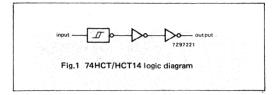

Another subset, the XX74HCUXXXXX, consists of single-stage unbuffered CMOS compatible devices for application in RC or crystal controlled oscillators and other types of feedback circuits which operate in the linear mode.

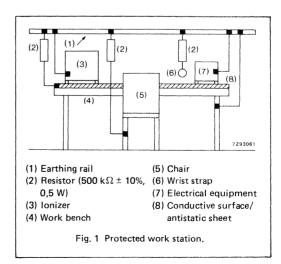

#### HANDLING MOS DEVICES

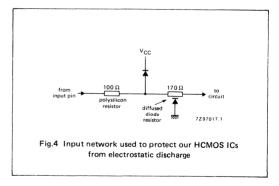

Inputs and outputs are protected against electrostatic effects in a wide variety of device-handling situations. However, to be totally safe, it is desirable to take handling precautions into account (see also chapter "HANDLING PRECAUTIONS").

#### **RECOMMENDED OPERATING CONDITIONS FOR 74HC/HCT**

| SYMBOL                          | PARAMETER                                                      |      | 74HC |                    |      | 74HCT |      | LIBUT | CONDITIONS                                                                    |

|---------------------------------|----------------------------------------------------------------|------|------|--------------------|------|-------|------|-------|-------------------------------------------------------------------------------|

| STMBOL                          | TANAMETEN                                                      | min. | typ. | max.               | min. | typ.  | max. | UNIT  | CONDITIONS                                                                    |

| vcc                             | DC supply voltage                                              | 2.0  | 5.0  | 6.0                | 4.5  | 5.0   | 5.5  | V     |                                                                               |

| Vį                              | DC input voltage range                                         | 0    |      | Vcc                | 0    |       | Vcc  | V     |                                                                               |

| v <sub>o</sub>                  | DC output voltage range                                        | 0    |      | VCC                | 0    |       | Vcc  | V     |                                                                               |

| T <sub>amb</sub>                | operating ambient temperature range                            | -40  |      | +85                | -40  |       | +85  | °C    | see DC and AC                                                                 |

| T <sub>amb</sub>                | operating ambient temperature range                            | -40  |      | +125               | -40  |       | +125 | °C    | CHAR.<br>per device                                                           |

| t <sub>r</sub> , t <sub>f</sub> | input rise and fall times<br>except for Schmitt-trigger inputs |      | 6.0  | 1000<br>500<br>400 |      | 6.0   | 500  | ns    | V <sub>CC</sub> = 2.0 V<br>V <sub>CC</sub> = 4.5 V<br>V <sub>CC</sub> = 6.0 V |

#### Note

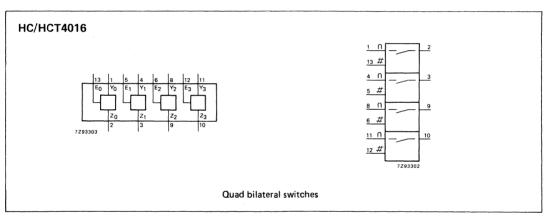

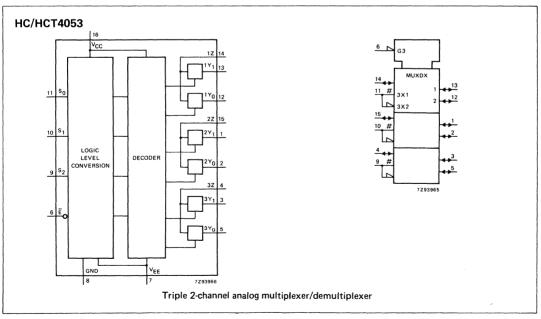

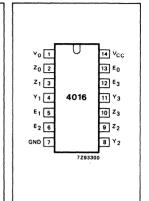

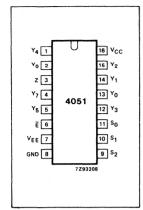

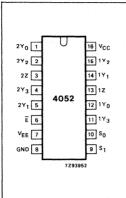

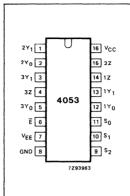

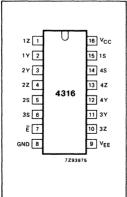

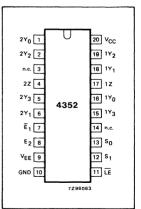

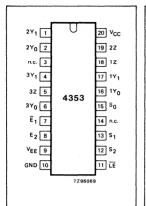

For analog switches, e.g. "4016", "4051 series", "4351 series", "4066" and "4067", 10 V is specified as the maximum operating voltage.

#### **RECOMMENDED OPERATING CONDITIONS FOR 74HCU**

| SYMBOL           | PARAMETER                           |      | 74HCL | J               | UNIT | CONDITIONS          |  |  |

|------------------|-------------------------------------|------|-------|-----------------|------|---------------------|--|--|

| STWIBUL          | FARAMETER                           | min. | typ.  | max.            | UNIT | CONDITIONS          |  |  |

| V <sub>CC</sub>  | DC supply voltage                   | 2.0  | 5.0   | 6.0             | V    |                     |  |  |

| V <sub>I</sub>   | DC input voltage range              | 0    |       | v <sub>cc</sub> | ٧    |                     |  |  |

| v <sub>O</sub>   | DC output voltage range             | 0    |       | Vcc             | V    |                     |  |  |

| T <sub>amb</sub> | operating ambient temperature range | -40  |       | +85             | °C   | see DC and AC       |  |  |

| T <sub>amb</sub> | operating ambient temperature range | -40  |       | +125            | °C   | CHAR.<br>per device |  |  |

# FAMILY SPECIFICATIONS

#### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Voltages are referenced to GND (ground = 0 V)

| SYMBOL           | PARAMETER                                                                                          | MIN. | MAX.     | UNIT     | CONDITIONS                                                                        |

|------------------|----------------------------------------------------------------------------------------------------|------|----------|----------|-----------------------------------------------------------------------------------|

| vcc              | DC supply voltage                                                                                  | -0.5 | +7       | V        |                                                                                   |

| <sup>±</sup> IK  | DC input diode current                                                                             |      | 20       | mA       | for $V_1 < -0.5$ or $V_1 > V_{CC} + 0.5$ V                                        |

| ±IOK             | DC output diode current                                                                            |      | 20       | mA       | for $V_{O}$ < $-0.5$ or $V_{O}$ > $V_{CC}$ +0.5 $V$                               |

| ±ΙΟ              | DC output source or sink current  - standard outputs  - bus driver outputs                         |      | 25<br>35 | mA<br>mA | for $-0.5 \text{ V} < \text{V}_{\text{O}} < \text{V}_{\text{CC}} + 0.5 \text{ V}$ |

| ±ICC;<br>±IGND   | DC V <sub>CC</sub> or GND current<br>for types with:<br>- standard outputs<br>- bus driver outputs |      | 50<br>70 | mA<br>mA |                                                                                   |

| T <sub>stg</sub> | storage temperature range                                                                          | -65  | +150     | °C       |                                                                                   |

| P <sub>tot</sub> | power dissipation per package                                                                      |      |          |          | for temperature range: -40 to +125 °C 74HC/HCT/HCU                                |

|                  | plastic DIL                                                                                        |      | 500      | mW       | above +70 °C: derate linearly with 8 mW/K                                         |

|                  | plastic mini-pack (SO)                                                                             |      | 400      | mW       | above +70 °C: derate linearly with 6 mW/K                                         |

#### Note

For analog switches, e.g. "4016", "4051 series", "4351 series", "4066" and "4067", 11 V is specified as the maximum operating voltage.

#### DC CHARACTERISTICS FOR 74HC

Voltages are referenced to GND (ground = 0 V)

|                  |                                                      |                    |                   | •                  | T <sub>amb</sub> ( | °C)                  |                    |                       |                | TEST CONDITIONS   |                                          |                                                                               |  |  |

|------------------|------------------------------------------------------|--------------------|-------------------|--------------------|--------------------|----------------------|--------------------|-----------------------|----------------|-------------------|------------------------------------------|-------------------------------------------------------------------------------|--|--|

|                  |                                                      |                    |                   |                    | 74H                | 3                    |                    |                       |                |                   |                                          |                                                                               |  |  |

| SYMBOL           | PARAMETER                                            |                    | +25               | 5                  | -40                | to +85               | -40 t              | o +125                | UNIT           | V <sub>CC</sub>   | VI                                       | OTHER                                                                         |  |  |

|                  |                                                      | min.               | typ.              | max.               | min.               | max.                 | min.               | max.                  |                |                   |                                          |                                                                               |  |  |

| v <sub>IH</sub>  | HIGH level input voltage                             | 1.5<br>3.15<br>4.2 | 1.2<br>2.4<br>3.2 |                    | 1.5<br>3.15<br>4.2 |                      | 1.5<br>3.15<br>4.2 |                       | ٧              | 2.0<br>4.5<br>6.0 |                                          |                                                                               |  |  |

| VIL              | LOW level input voltage                              |                    | 0.8<br>2.1<br>2.8 | 0.5<br>1.35<br>1.8 |                    | 0.5<br>1.35<br>1.8   |                    | 0.5<br>1.35<br>1.8    | V              | 2.0<br>4.5<br>6.0 |                                          |                                                                               |  |  |

| Vон              | HIGH level output voltage all outputs                | 1.9<br>4.4<br>5.9  | 2.0<br>4.5<br>6.0 |                    | 1.9<br>4.4<br>5.9  |                      | 1.9<br>4.4<br>5.9  |                       | ٧              | 2.0<br>4.5<br>6.0 | VIH<br>or<br>VIL                         | -I <sub>O</sub> = 20 μA<br>-I <sub>O</sub> = 20 μA<br>-I <sub>O</sub> = 20 μA |  |  |

| Vон              | HIGH level output voltage standard outputs           | 3.98<br>5.48       |                   |                    | 3.84<br>5.34       |                      | 3.7<br>5.2         |                       | V              | 4.5<br>6.0        | VIH<br>or<br>VIL                         | -I <sub>O</sub> = 4.0 mA<br>-I <sub>O</sub> = 5.2 mA                          |  |  |

| V <sub>OH</sub>  | HIGH level output voltage bus driver outputs         | 3.98<br>5.48       | 4.32<br>5.81      |                    | 3.84<br>5.34       |                      | 3.7<br>5.2         |                       | ٧              | 4.5<br>6.0        | VIH<br>or<br>VIL                         | -I <sub>O</sub> = 6.0 mA<br>-I <sub>O</sub> = 7.8 mA                          |  |  |

| VOL              | LOW level output voltage all outputs                 |                    | 0<br>0<br>0       | 0.1<br>0.1<br>0.1  |                    | 0.1<br>0.1<br>0.1    |                    | 0.1<br>0.1<br>0.1     | V              | 2.0<br>4.5<br>6.0 | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA    |  |  |

| VOL              | LOW level output voltage standard outputs            |                    | 0.15<br>0.16      | 0.26<br>0.26       |                    | 0.33<br>0.33         |                    | 0.4<br>0.4            | ٧              | 4.5<br>6.0        | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 4.0 mA<br>I <sub>O</sub> = 5.2 mA                            |  |  |

| VOL              | LOW level output voltage bus driver outputs          |                    | 0.15<br>0.16      |                    |                    | 0.33<br>0.33         |                    | 0.4<br>0.4            | V              | 4.5<br>6.0        | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 6.0 mA<br>I <sub>O</sub> = 7.8 mA                            |  |  |

| ±Iį              | input leakage current                                |                    |                   | 0.1                |                    | 1.0                  |                    | 1.0                   | μΑ             | 6.0               | V <sub>CC</sub><br>or<br>GND             |                                                                               |  |  |

| ±I <sub>OZ</sub> | 3-state OFF-state current                            |                    |                   | 0.5                |                    | 5.0                  |                    | 10.0                  | μА             | 6.0               | VIH<br>or<br>VIL                         | V <sub>O</sub> = V <sub>CC</sub><br>or GND                                    |  |  |

| lcc              | quiescent supply current<br>SSI<br>flip-flops<br>MSI |                    |                   | 2.0<br>4.0<br>8.0  |                    | 20.0<br>40.0<br>80.0 |                    | 40.0<br>80.0<br>160.0 | μΑ<br>μΑ<br>μΑ | 6.0<br>6.0<br>6.0 | VCC<br>or<br>GND                         | IO = 0                                                                        |  |  |

# FAMILY SPECIFICATIONS

#### DC CHARACTERISTICS FOR 74HCT

Voltages are referenced to GND (ground = 0 V)

|                  |                                                                                                    |      |      |                   | T <sub>amb</sub> ( | °C)                  |       |                       |                | TEST CONDITIONS   |                                          |                                                                                                                              |  |  |

|------------------|----------------------------------------------------------------------------------------------------|------|------|-------------------|--------------------|----------------------|-------|-----------------------|----------------|-------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| SYMBOL           | PARAMETER                                                                                          |      |      |                   | 74HC               | т                    | •     |                       | UNIT           | Vcc               | Vi                                       | OTHER                                                                                                                        |  |  |

| STINIBUL         | PARAMETER                                                                                          |      | +25  |                   | -401               | to +85               | -40 t | o +125                | ONT            | VCC               | V1                                       | OTHER                                                                                                                        |  |  |

|                  |                                                                                                    | min. | typ. | max.              | min.               | max.                 | min.  | max.                  |                |                   |                                          |                                                                                                                              |  |  |

| V <sub>IH</sub>  | HIGH level input voltage                                                                           | 2.0  | 1.6  |                   | 2.0                |                      | 2.0   |                       | v              | 4.5<br>to<br>5.5  |                                          |                                                                                                                              |  |  |

| VIL              | LOW level input voltage                                                                            |      | 1.2  | 0.8               |                    | 0.8                  |       | 0.8                   | v              | 4.5<br>to<br>5.5  |                                          |                                                                                                                              |  |  |

| Vон              | HIGH level output voltage all outputs                                                              | 4.4  | 4.5  |                   | 4.4                |                      | 4.4   |                       | *V             | 4.5               | VIH<br>or<br>VIL                         | -I <sub>O</sub> = 20 μA                                                                                                      |  |  |

| Voн              | HIGH level output voltage standard outputs                                                         | 3.98 | 4.32 |                   | 3.84               |                      | 3.7   | -                     | V              | 4.5               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | -I <sub>O</sub> = 4.0 mA                                                                                                     |  |  |

| Voн              | HIGH level output voltage<br>bus driver outputs                                                    | 3.98 | 4.32 |                   | 3.84               |                      | 3.7   |                       | V              | 4.5               | VIH<br>or<br>VIL                         | -I <sub>O</sub> = 6.0 mA                                                                                                     |  |  |

| VOL              | LOW level output voltage all outputs                                                               |      | 0    | 0.1               |                    | 0.1                  |       | 0.1                   | ٧              | 4.5               | VIH<br>or<br>VIL                         | Ι <sub>Ο</sub> = 20 μΑ                                                                                                       |  |  |

| VOL              | LOW level output voltage standard outputs                                                          |      | 0.15 | 0.26              |                    | 0.33                 |       | 0.4                   | ٧              | 4.5               | VIH<br>or<br>VIL                         | I <sub>O</sub> = 4.0 mA                                                                                                      |  |  |

| VOL              | LOW level output voltage bus driver outputs                                                        |      | 0.16 | 0.26              |                    | 0.33                 |       | 0.4                   | ٧              | 4.5               | VIH<br>or<br>VIL                         | I <sub>O</sub> = 6.0 mA                                                                                                      |  |  |

| ±II              | input leakage current                                                                              |      |      | 0.1               |                    | 1.0                  |       | 1.0                   | μΑ             | 5.5               | V <sub>CC</sub><br>or<br>GND             |                                                                                                                              |  |  |

| ±IOZ             | 3-state OFF-state current                                                                          |      |      | 0.5               |                    | 5.0                  |       | 10.0                  | μΑ             | 5.5               | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | V <sub>O</sub> =V <sub>CC</sub> or GND<br>per input pin;<br>other inputs at<br>V <sub>CC</sub> or GND;<br>I <sub>O</sub> = 0 |  |  |

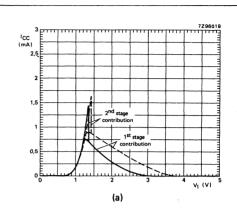

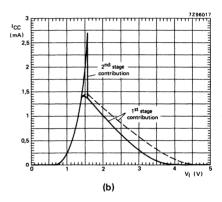

| Icc              | quiescent supply current<br>SSI<br>flip-flops<br>MSI                                               |      |      | 2.0<br>4.0<br>8.0 |                    | 20.0<br>40.0<br>80.0 |       | 40.0<br>80.0<br>160.0 | μΑ<br>μΑ<br>μΑ | 5.5<br>5.5<br>5.5 | V <sub>CC</sub><br>or<br>GND             | I <sub>O</sub> = 0                                                                                                           |  |  |

| ΔI <sub>CC</sub> | additional quiescent supply<br>current per input pin for<br>unit load coefficient is 1<br>(note 1) |      | 100  | 360               |                    | 450                  |       | 490                   | μΑ             | 4.5<br>to<br>5.5  | V <sub>CC</sub><br>-2.1 V                | other inputs at V <sub>CC</sub> or GND; I <sub>O</sub> = 0                                                                   |  |  |

#### Note

The additional quiescent supply current per input is determined by the ΔI<sub>CC</sub> unit load, which has to be multiplied by the unit load coefficient as given in the individual data sheets. For dual supply systems the theoretical worst-case (V<sub>1</sub> = 2.4 V; V<sub>CC</sub> = 5.5 V) specification is: ΔI<sub>CC</sub> = 0.65 mA (typical) and 1.8 mA (maximum) across temperature.

#### DC CHARACTERISTICS FOR 74HCU

Voltages are referenced to GND (ground = 0 V)

|                 |                                 |                   |                   | •                 | T <sub>amb</sub> ( | °C)               | -12               |                   |      | TEST CONDITIONS   |                                          |                                                                            |  |  |  |

|-----------------|---------------------------------|-------------------|-------------------|-------------------|--------------------|-------------------|-------------------|-------------------|------|-------------------|------------------------------------------|----------------------------------------------------------------------------|--|--|--|

| SYMBOL          | PARAMETER                       |                   |                   |                   | 74HC               | :U                |                   |                   | UNIT |                   | V <sub>i</sub>                           | OTHER                                                                      |  |  |  |

| STINBUL         | PANAMETER                       |                   | +25               |                   | -40                | to +85            | -40 t             | o +125            | UNIT | VCC               | V 1                                      | OTHER                                                                      |  |  |  |

|                 |                                 | min.              | typ.              | max.              | min.               | max.              | min.              | max.              |      |                   |                                          |                                                                            |  |  |  |

| V <sub>IH</sub> | HIGH level input voltage        | 1.7<br>3.6<br>4.8 | 1.4<br>2.6<br>3.4 |                   | 1.7<br>3.6<br>4.8  |                   | 1.7<br>3.6<br>4.8 |                   | ٧    | 2.0<br>4.5<br>6.0 |                                          |                                                                            |  |  |  |

| VIL             | LOW level input voltage         |                   | 0.6<br>1.9<br>2.6 | 0.3<br>0.9<br>1.2 |                    | 0.3<br>0.9<br>1.2 |                   | 0.3<br>0.9<br>1.2 | ٧    | 2.0<br>4.5<br>6.0 |                                          |                                                                            |  |  |  |

| Vон             | HIGH level output voltage       | 1.8<br>4.0<br>5.5 | 2.0<br>4.5<br>6.0 |                   | 1.8<br>4.0<br>5.5  |                   | 1.8<br>4.0<br>5.5 |                   | v    | 2.0<br>4.5<br>6.0 | VIH<br>or<br>VIL                         | $-I_O = 20 \mu A$<br>$-I_O = 20 \mu A$<br>$-I_O = 20 \mu A$                |  |  |  |

| V <sub>ОН</sub> | HIGH level output voltage       | 3.98<br>5.48      | 4.32<br>5.81      |                   | 3.84<br>5.34       |                   | 3.7<br>5.2        |                   | V    | 4.5<br>6.0        | V <sub>CC</sub><br>or<br>GND             | -I <sub>O</sub> = 4.0 mA<br>-I <sub>O</sub> = 5.2 mA                       |  |  |  |

| VOL             | LOW level output voltage        |                   | 0<br>0<br>0       | 0.2<br>0.5<br>0.5 |                    | 0.2<br>0.5<br>0.5 |                   | 0.2<br>0.5<br>0.5 | V    | 2.0<br>4.5<br>6.0 | V <sub>IH</sub><br>or<br>V <sub>IL</sub> | I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA<br>I <sub>O</sub> = 20 μA |  |  |  |

| VOL             | LOW level output voltage        |                   | 0.15<br>0.16      | 0.26<br>0.26      |                    | 0.33<br>0.33      |                   | 0.4<br>0.4        | v    | 4.5<br>6.0        | V <sub>CC</sub><br>or<br>GND             | I <sub>O</sub> = 4.0 mA<br>I <sub>O</sub> = 5.2 mA                         |  |  |  |

| ±II             | input leakage current           |                   | -                 | 0.1               |                    | 1.0               |                   | 1.0               | μА   | 6.0               | V <sub>CC</sub><br>or<br>GND             |                                                                            |  |  |  |

| Icc             | quiescent supply current<br>SSI |                   |                   | 2.0               |                    | 20.0              |                   | 40.0              | μΑ   | 6.0               | V <sub>CC</sub><br>or<br>GND             | I <sub>O</sub> = 0                                                         |  |  |  |

# FAMILY SPECIFICATIONS

#### **AC CHARACTERISTICS FOR 74HC**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                                   |                                              |           |              |                | T <sub>amb</sub> ( | °C)            |       |                 |           |                   | TEST CONDITIONS |

|---------------------------------------------------|----------------------------------------------|-----------|--------------|----------------|--------------------|----------------|-------|-----------------|-----------|-------------------|-----------------|

| CVMDOL                                            | DADAMETED                                    | 74HC UNIT |              |                |                    |                |       |                 | WAVEFORMS |                   |                 |

| SYMBOL                                            | PARAMETER                                    |           | +25          |                | -40                | to +85         | -40 t | o +125          | UNII      | VCC               | WAVEFORMS       |

|                                                   |                                              | min.      | typ.         | max.           | min.               | max.           | min.  | max.            |           |                   | *               |

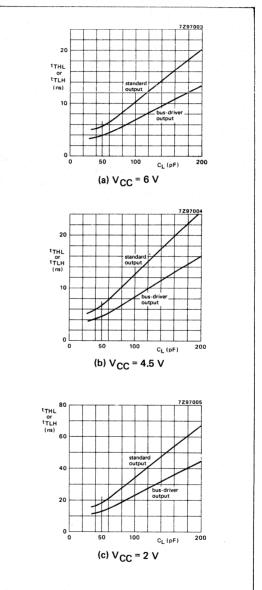

| t <sub>THL</sub> /<br>t <sub>TLH</sub>            | output transition time<br>standard outputs   |           | 19<br>7<br>6 | 75<br>15<br>13 |                    | 95<br>19<br>16 |       | 110<br>22<br>19 | ns        | 2.0<br>4.5<br>6.0 | Figs 3 and 4    |

| <sup>t</sup> THL <sup>/</sup><br><sup>t</sup> TLH | output transition time<br>bus driver outputs |           | 14<br>5<br>4 | 60<br>12<br>10 | . 1                | 75<br>15<br>13 | -     | 90<br>18<br>15  | ns        | 2.0<br>4.5<br>6.0 | Figs 3 and 4    |

#### **AC CHARACTERISTICS FOR 74HCU**

GND = 0 V;  $t_r = t_f = 6 \text{ ns}$ ;  $C_L = 50 \text{ pF}$

|                                        |                        |      |              |                | T <sub>amb</sub> ( | °C)            |       |                 |      | TEST CONDITIONS   |           |  |

|----------------------------------------|------------------------|------|--------------|----------------|--------------------|----------------|-------|-----------------|------|-------------------|-----------|--|

| SYMBOL                                 | PARAMETER              |      |              |                | 74H0               | U              |       |                 | UNIT | Vaa               | WAVEFORMS |  |

| STIMBOL                                | PANAMETER              |      | +25          |                | -40                | to +85         | -40 t | o +125          | UNII | VCC               | WAVEFORMS |  |

|                                        |                        | min. | typ.         | max.           | min.               | max.           | min.  | max.            |      |                   |           |  |

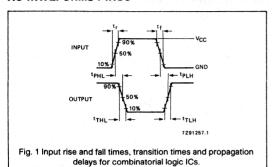

| t <sub>THL</sub> /<br>t <sub>TLH</sub> | output transition time | ·    | 19<br>7<br>6 | 75<br>15<br>13 |                    | 95<br>19<br>16 |       | 110<br>22<br>19 | ns   | 2.0<br>4.5<br>6.0 | Fig. 1    |  |

#### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_r = t_f = 6 ns; C_L = 50 pF$

|                                        | ·                                            |      |      |      | T <sub>amb</sub> ( | °C)    | ····· |        |      | TEST CONDITIONS |              |  |  |

|----------------------------------------|----------------------------------------------|------|------|------|--------------------|--------|-------|--------|------|-----------------|--------------|--|--|

| CVMDOL                                 | PARAMETER                                    |      |      |      | 74H                | т      |       | UNIT   | V    | WAVEFORMS       |              |  |  |

| SYMBOL                                 | PARAMETER                                    |      | +25  |      | -40                | to +85 | -40 t | o +125 | UNIT | V <sub>CC</sub> | WAVEFORMS    |  |  |

|                                        |                                              | min. | typ. | max. | min.               | max.   | min.  | max.   |      |                 |              |  |  |

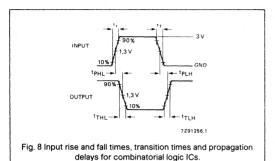

| t <sub>THL</sub> /<br>t <sub>TLH</sub> | output transition time<br>standard outputs   |      | 7    | 15   |                    | 19     |       | 22     | ns   | 4.5             | Figs 8 and 9 |  |  |

| tTHL/<br>tTLH                          | output transition time<br>bus driver outputs |      | 5    | 12   | -                  | 15     |       | 18     | ns   | 4.5             | Figs 8 and 9 |  |  |

#### **HCU TYPES**

#### **AC WAVEFORMS 74HCU**

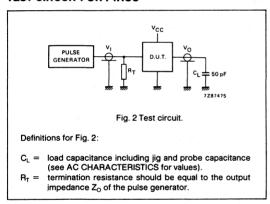

#### **TEST CIRCUIT FOR 74HCU**

#### HC TYPES

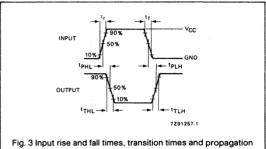

#### **AC WAVEFORMS 74HC**

delays for combinatorial logic ICs.

#### **AC WAVEFORMS 74HC**

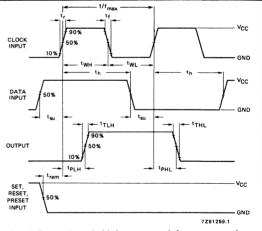

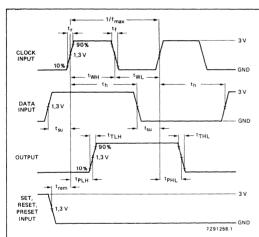

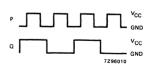

Fig. 4 Set-up times, hold times, removal times, propagation delays and the maximum clock pulse frequency for sequential logic ICs.

#### Notes to Fig. 4

- 1. In Fig. 4 the active transition of the clock is going from LOWto-HIGH and the active level of the forcing signals (SET, RESET and PRESET) is HIGH. The actual direction of the transition of the clock input and the actual active levels of the forcing signals are specified in the individual device data sheet.

- 2. For AC measurements:  $t_r = t_f = 6$  ns; when measuring  $f_{max}$ , there is no constraint on tr, tf with 50% duty factor.

# FAMILY SPECIFICATIONS

#### **HC TYPES (continued)**

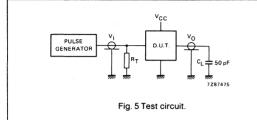

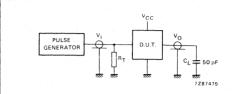

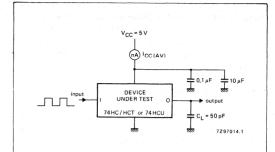

#### **TEST CIRCUIT FOR 74HC**

#### Definitions for Fig. 5:

$C_L = \mbox{load capacitance including jig and probe capacitance}$  (see AC CHARACTERISTICS for values).

$R_T =$  termination resistance should be equal to the output impedance  $Z_O$  of the pulse generator.

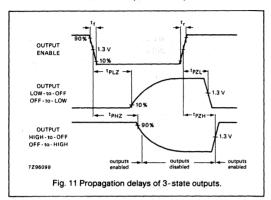

#### **AC WAVEFORMS 74HC (continued)**

#### **TEST CIRCUIT FOR 74HC**

#### **Switch position**

| TEST             | SWITCH          |

|------------------|-----------------|

| t <sub>PZH</sub> | GND             |

| t <sub>PZL</sub> | V <sub>CC</sub> |

| t <sub>PHZ</sub> | GND             |

| t <sub>PLZ</sub> | V <sub>CC</sub> |

#### Note to switch position table

For open-drain N-channel outputs  $t_{\text{PLZ}}$  and  $t_{\text{PZL}}$  are applicable.

Fig. 7 Test circuit for 3-state outputs.

Definitions for Fig. 7:

$C_L = \mbox{load capacitance including jig and probe capacitance} \mbox{(see AC CHARACTERISTICS for values)}.$

$R_T = {}^{\dagger}$  termination resistance should be equal to the output impedance  $Z_O$  of the pulse generator.

#### **HCT TYPES**

#### **AC WAVEFORMS 74HCT**

#### **AC WAVEFORMS 74HCT**

Fig. 9 Set-up times, hold times, removal times, propagation delays and the maximum clock pulse frequency for sequential logic ICs.

#### Notes to Fig. 9

- In Fig. 9 the active transition of the clock is going from LOWto-HIGH and the active level of the forcing signals (SET, RESET and PRESET) is HIGH. The actual direction of the transition of the clock input and the actual active levels of the forcing signals are specified in the individual device data sheet.

- 2. For AC measurements:  $t_r$  =  $t_f$  = 6 ns; when measuring  $f_{max}$ , there is no constraint on  $t_r$ ,  $t_f$  with 50% duty factor.

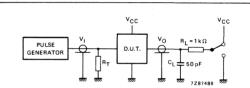

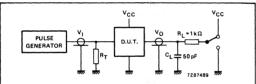

#### **TEST CIRCUIT FOR 74HCT**

Fig. 10 Test circuit.

#### Definitions for Fig. 10:

- C<sub>L</sub> = load capacitance including jig and probe capacitance (see AC CHARACTERISTICS for values).

- $R_T$  = termination resistance should be equal to the output impedance  $Z_O$  of the pulse generator.

#### FAMILY SPECIFICATIONS

#### **HCT TYPES** (continued)

#### **AC WAVEFORMS 74HCT (continued)**

#### **TEST CIRCUIT FOR 74HCT**

#### **Switch position**

| TEST             | SWITCH          |

|------------------|-----------------|

| t <sub>PZH</sub> | GND             |

| t <sub>PZL</sub> | V <sub>CC</sub> |

| t <sub>PHZ</sub> | GND             |

| t <sub>PLZ</sub> | V <sub>CC</sub> |

#### Note to switch position table

For open-drain N-channel outputs  $t_{\text{PLZ}}$  and  $t_{\text{PZL}}$  are applicable.

Fig. 12 Test circuit for 3-state outputs.

Definitions for Fig. 12:

$\mathbf{C_L} = \begin{array}{ll} \text{load capacitance including jig and probe capacitance} \\ \text{(see AC CHARACTERISTICS for values).} \end{array}$

$R_T=\displaystyle{\begin{array}{c} termination\ resistance\ should\ be\ equal\ to\ the\ output\ impedance\ Z_O\ of\ the\ pulse\ generator. \end{array}}$

#### INTRODUCTION

The 74HCMOS data sheets have been designed for ease-ofuse. A minimum of cross-referencing for more information is needed.

#### TYPICAL PROPAGATION DELAY AND FREQUENCY

The typical propagation delays listed at the top of the data sheets are the average of tp<sub>LH</sub> and tp<sub>HL</sub> for the longest data path through the device with a 15 pF load.

For clocked devices, the maximum frequency of operation is also given. The typical operating frequency is the maximum device operating frequency with a 50% duty factor and no constraints on  $t_r$  and  $t_f$ .

#### LOGIC SYMBOLS

Two logic symbols are given for each device — the conventional one (Logic Symbol) which explicitly shows the internal logic (except for complex logic) and the IEC Logic Symbol as developed by the IEC (International Electrotechnical Commission).

The IEC has been developing a very powerful symbolic language that can show the relationship of each input of a digital logic current to each output without explicitly showing the internal logic. Internationally, Working Group 2 of IEC Technical Committee TC-3 has prepared a new document (Publication 617-12) which supersedes Publication 117-15, published in 1972.

#### RATINGS

The "RATINGS" table (Limiting values in accordance with the Absolute Maximum System — IEC134) lists the maximum limits to which the device can be subjected without damage. This doesn't imply that the device will function at these extreme conditions, only that, when these conditions are removed and the device operated within the Recommended Operating Conditions, it will still be functional and its useful life won't have been shortened.

The maximum rated supply voltage of 7 V is well below the typical breakdown voltage of 18 V.

#### RECOMMENDED OPERATING CONDITIONS

The "RECOMMENDED OPERATING CONDITIONS" table lists the operating ambient temperature and the conditions under which the limits in the "DC CHARAC-TERISTICS" and "AC CHARACTERISTICS" tables will be met. The table should not be seen as a set of limits guaranteed by the manufacturer, but as the conditions used to test the devices and guarantee that they will then meet the limits in the DC and AC CHARACTERISTICS tables.

#### DC CHARACTERISTICS

The "DC CHARACTERISTICS" table reflects the DC limits used during testing. The values published are guaranteed.

The threshold values of VIH and VII can be tested by the user. If VIH and VII are applied to the inputs, the output voltages will be those published in the "DC CHARACTER-ISTICS" table. There is a tendency, by some, to use the published  $V_{IH}$  and  $V_{II}$  thresholds to test a device for functionality in a "function-table exercizer" mode. This frequently causes problems because of the noise present at the test head of automated test equipment with cables up to 1 metre. Parametric tests, such as those used for the output levels under the VIH and VII conditions are done fairly slowly, in the order of milliseconds, so that there is no noise at the inputs when the outputs are measured. But in functionality testing, the outputs are measured much faster, so there can be noise on the inputs, before the device has assumed its final and correct output state. Thus, never use VIH and VII to test the functionality of any HCMOS device type; instead, use input voltages of VCC (for the HIGH state) and 0 V (for the LOW state). In no way does this imply that the devices are noise-sensitive in the final system.

In the data sheets, it may appear strange that the typical  $V_{1L}$  is higher than the maximum  $V_{1L}$ . However, this is because  $V_{1Lmax}$  is the maximum  $V_{1L}$  (guaranteed) for all devices that will be recognized as a logic LOW. However, typically a higher  $V_{1L}$  will also be recognized as a logic LOW. Conversely, the typical  $V_{1H}$  is lower than its minimum guaranteed level.

For 74HCMOS, unlike TTL, no output HIGH short-circuit current is specified. The use of this current, for example, to calculate propagation delays with capacitive loads, is covered by the HCMOS graphs showing the output drive capability and those showing the dependence of propagation delay on load capacitance.

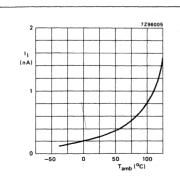

The quiescent supply current  $I_{CC}$  is the leakage current of all the reversed-biased diodes and the OFF-state MOS transistors. It is measured with the inputs at  $V_{CC}$  or GND and is typically a few nA.

#### **AC CHARACTERISTICS**

The "AC CHARACTERISTICS" table lists the guaranteed limits when a device is tested under the conditions given in the AC Test Circuits and Waveforms section.

#### DATA SHEET SPECIFICATION GUIDE

#### **TEST CIRCUITS**

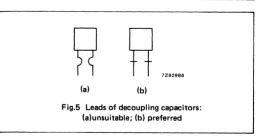

Good high-frequency wiring practices should be used in test circuits. Capacitor leads should be as short as possible to minimize ripples on the output waveform transitions and undershoot. Generous ground metal (preferably a groundplane) should be used for the same reasons. A  $V_{\mbox{\scriptsize CC}}$  decoupling capacitor should be provided at the test socket, also with short leads. Input signals should have rise and fall times of 6 ns, a signal swing of 0 V to V<sub>CC</sub> for 74HC and OV to 3V for 74HCT; a 1.0 MHz square wave is recommended for most propagation delay tests. The repetition rate must be increased for testing  $f_{\mbox{\scriptsize max}}$ . Two pulse generators are usually required for testing such parameters as set-up time, hold time and removal time. fmax is also tested with 6ns input rise and fall times, with a 50% duty factor, but for typical fmax as high as 60 MHz, there are no constraints on rise and fall times.

# DEFINITIONS OF SYMBOLS AND TERMS USED IN HCMOS DATA SHEETS

#### Currents

Positive current is defined as conventional current flow into a device.

Negative current is defined as conventional current flow out of a device.

| lcc | Quiescent power supply current; the current flowing into |

|-----|----------------------------------------------------------|

|     | the V <sub>CC</sub> supply terminal.                     |

$\Delta I_{CC}$  Additional quiescent supply current per input pin at a specified input voltage and  $V_{CC}$ .

I<sub>GND</sub> Quiescent power supply current; the current flowing into the GND terminal.

Input leakage current; the current flowing into a device at a specified input voltage and V<sub>CC</sub>.

I<sub>IK</sub> Input diode current; the current flowing into a device at a specified input voltage.

I<sub>O</sub> Output source or sink current; the current flowing into a device at a specified output voltage.

I<sub>OK</sub> Output diode current; the current flowing into a device at a specified output voltage.

I<sub>OZ</sub> OFF-state output current; the leakage current flowing into the output of a 3-state device in the OFF-state, when the output is connected to V<sub>CC</sub> or GND.

$I_S \qquad \text{Analog switch leakage current; the current flowing into an analog switch at a specified voltage across the switch and $V_{\rm CC}$.}$

#### **Voltages**

All voltages are referenced to GND (ground), which is typically 0 V.

GND Supply voltage; for a device with a single negative power supply, the most negative power supply, used as the reference level for other voltages; typically ground.

V<sub>CC</sub> Supply voltage; the most positive potential on the device.

V<sub>EE</sub> Supply voltage; one of two (GND and V<sub>EE</sub>) negative power supplies.

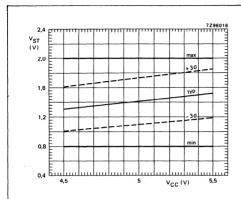

V<sub>H</sub> Hysteresis voltage; difference between the trigger levels, when applying a positive and a negative - going input signal.

V<sub>IH</sub> HIGH level input voltage; the range of input voltages that represents a logic HIGH level in the system.

V<sub>IL</sub> LOW level input voltage; the range of input voltages that represents a logic LOW level in the system.

V<sub>OH</sub> HIGH level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage. Device inputs are conditioned to establish a HIGH level at the output.

Vol.

LOW level output voltage; the range of voltages at an output terminal with a specified output loading and supply voltage.

Device inputs are conditioned to establish a LOW level at the output.

V<sub>T+</sub> Trigger threshold voltage; positive-going signal.

V<sub>T</sub> Trigger threshold voltage; negative-going signal.

#### **Analog terms**

R<sub>ON</sub> ON-resistance; the effective ON-state resistance of an analog switch, at a specified voltage across the switch and output load.

ΔR<sub>ON</sub> ΔON-resistance; the difference in ON-resistance between any two switches of an analog device at a specified voltage across the switch and output load.

#### Capacitances

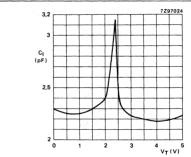

C<sub>1</sub> Input capacitance; the capacitance measured at a terminal connected to an input of a device.

C<sub>I/O</sub> Input/Output capacitance; the capacitance measured at a terminal connected to an I/O-pin (e.g. a transceiver).

C<sub>L</sub> Output load capacitance; the capacitance connected to an output terminal including jig and probe capacitance.

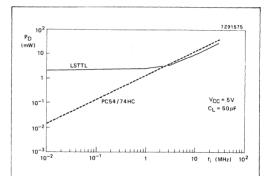

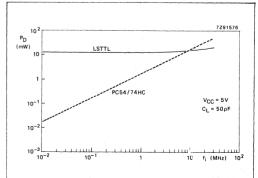

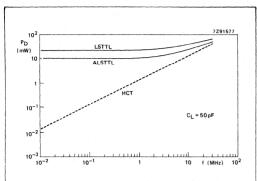

C<sub>PD</sub> Power dissipation capacitance; the capacitance used to determine the dynamic power dissipation per logic function, when no extra load is provided to the device.

C<sub>S</sub> Switch capacitance; the capacitance of a terminal to a switch of an analog device.

#### **AC switching parameters**

Input frequency; for combinatorial logic devices the maximum number of inputs and outputs switching in accordance with the device function table. For sequential logic devices the clock frequency using alternate HIGH and LOW for data input or using the toggle mode, whichever is applicable.

f<sub>o</sub> Output frequency; each output.

$f_{\text{max}}$  Maximum clock frequency; clock input waveforms should have a 50% duty factor and be such as to cause the outputs to be switching from  $10\% V_{\text{CC}}$  to  $90\% V_{\text{CC}}$  in accordance with the device function table.

Hold time; the interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure their continued recognition. A negative hold time indicates that the correct logic level may be released prior to the timing pulse and still be recognized.

t<sub>r</sub>, Clock input rise and fall times; 10% and 90% values.

t

#### AC switching parameters (continued)

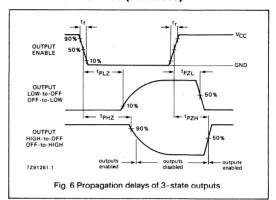

- tpHL Propagation delay; the time between the specified reference points, normally the 50% points for 74HC and 74HCU devices on the input and output waveforms and the 1.3 V points for the 74HCT devices, with the output changing from the defined HIGH level to the defined LOW level.

- tplh Propagation delay; the time between the specified reference points, normally the 50% points for 74HC and 74HCU devices on the input and output waveforms and the 1.3 V point for the 74HCT devices, with the output changing from the defined LOW level to the defined HIGH level.

- tpHZ

3-state output disable time; the time between the specified reference points, normally the 50% points for the 74HC and 74HCU devices and the 1.3 V points for the 74HCT devices on the output enable input voltage waveform and a point representing 10% of the output swing on the output voltage waveform of a 3-state device, with the output changing from a HIGH level (V<sub>OH</sub>) to a high impedance OFF-state (Z).

- tpLZ

3-state output disable time; the time between the specified reference points, normally the 50% points for the 74HC devices and the 1.3 V points for the 74HCT devices on the output enable input voltage waveform and a point representing 10% of the output swing on the output voltage waveform of a 3-state device, with the output changing from a LOW level (VOL) to a high impedance OFF-state (Z).

- tpzh 3-state output enable time; the time between the specified reference points, normally the 50% points for the 74HC devices and 1.3 V points for the 74HCT devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-state device, with the output changing from a high impedance OFF-state (Z) to a HIGH level (VOH).

- tpzl 3-state output enable time; the time between the specified reference points, normally the 50% points for the 74HC devices and the 1.3 V points for the 74HCT devices on the output enable input voltage waveform and the 50% point on the output voltage waveform of a 3-state device, with the output changing from a high impedance OFF-state (Z) to a LOW level (VOI).

- t<sub>rem</sub> Removal time; the time between the end of an overriding asynchronous input, typically a clear or reset input, and the earliest permissible beginning of a synchronous control input, typically a clock input, normally measured at the 50% points for 74HC devices and the 1.3 V points for the 74HCT devices on both input voltage waveforms.

- t<sub>SU</sub> Set-up time; the interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the coltrol input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure their recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

- t<sub>THL</sub> Output transition time; the time between two specified reference points on a waveform, normally 90% and 10% points, that is changing from HIGH-to-LOW.

- t<sub>THL</sub> Output transition time; the time between two specified reference points on a waveform, normally 10% and 90% points, that is changing from LOW-to-HIGH.

- tw Pulse width; the time between the 50% amplitude points on the leading and trailing edges of a pulse for 74HC and 74HCU devices and at the 1.3 V points for 74HCT devices.

### **USER GUIDE**

|                                                     | page |

|-----------------------------------------------------|------|

| Introduction                                        | 24   |

| Construction                                        | 26   |

| AC characteristics                                  |      |

| Test conditions                                     |      |

| Comparing the speed of HCMOS and LSTTL              |      |

| Propagation delays and transition times             |      |

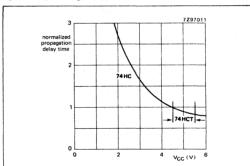

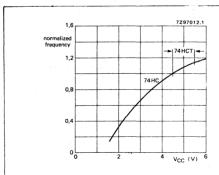

| Supply voltage dependence of propagation delay      |      |

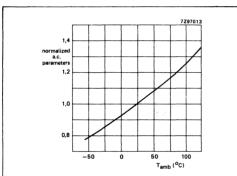

| Temperature dependence of propagation delay.        |      |

| Derating system for a.c. characteristics            |      |

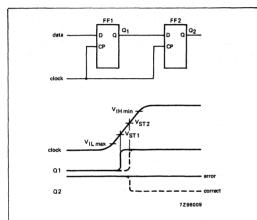

| Clock pulse requirements                            |      |

| System (parallel) clocking                          |      |

| Minimum a.c. characteristics                        | 31   |

| B. C. P. Smith                                      |      |

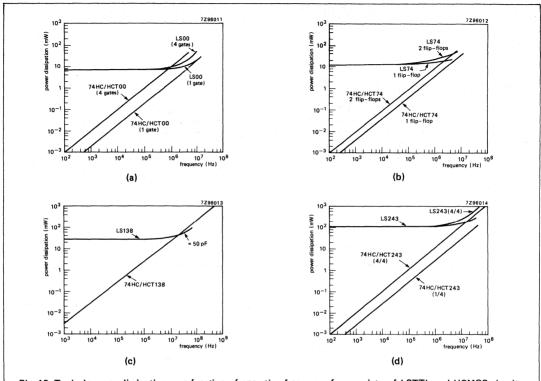

| Power dissipation                                   | 31   |

| Static                                              |      |

| Power dissipation capacitance                       |      |

| Conditions for CpD tests                            |      |

| Additional power dissipation in 74HCT devices       |      |

| Power dissipation due to slow input rise/fall times | 38   |

| Comparison with LSTTL power dissipation             |      |

| Companies with 25 to 2 power and participation      |      |

| Supply voltage                                      |      |

| Range                                               | 40   |

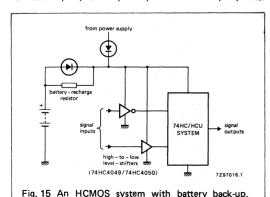

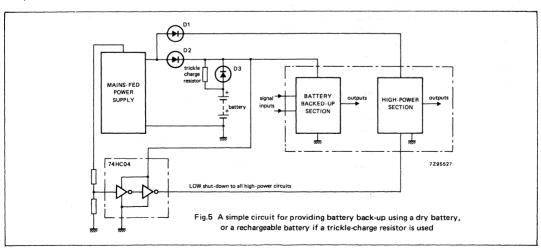

| Battery back-up                                     |      |

| Power supply regulation and decoupling              | 41   |

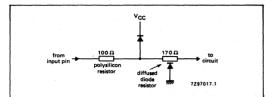

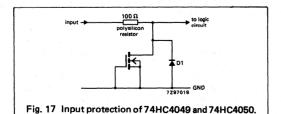

| Input/output protection                             | 41   |

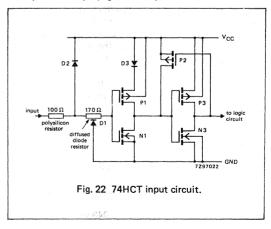

| Input circuits                                      |      |

| 74HC inputs                                         | 43   |

| 74HCT inputs                                        |      |

| Maximum input rise/fall times                       |      |

| Termination of unused inputs                        |      |

| Input current                                       |      |

| Input capacitance                                   |      |

| Coupling of adjacent inputs                         |      |

| Input voltage and forward diode input current       |      |

| O                                                   |      |

| Output drive                                        | AC   |

| Output drive                                        |      |

| Push-pull outputs                                   |      |

| Three-state outputs                                 |      |

| Increased drive capability of gates                 |      |

| Output capacitance                                  |      |

| Output capacitance                                  |      |

|                             |     |               | page     |

|-----------------------------|-----|---------------|----------|

| Static noise immunity       |     |               | 51       |

| Dynamic noise immunity      |     |               | 52       |

| Buffered devices            |     |               | <b>.</b> |

| Definition                  |     |               | 54       |

| Input buffering             |     | • • • • • • • | 54       |

| Performance of oscillators  |     |               | 55       |

| _atch-up free               |     |               | 55       |

| Orop-in replacements for LS | TTL |               | 55       |

| Bus systems                 |     |               | 56       |

| Package pin capacitance     |     |               | 57       |

**Note:** The information in this user guide is intended as a design-aid and does not constitute a guarantee.

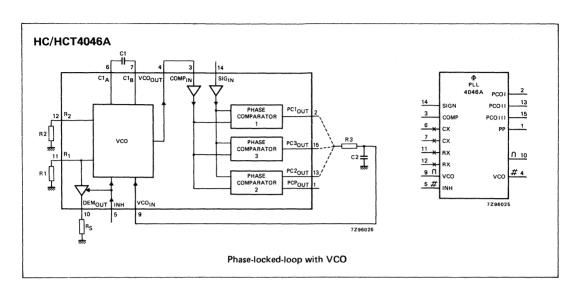

#### INTRODUCTION

The 74HC/HCT/HCU family is a comprehensive range of high-speed CMOS (HCMOS) integrated circuits. Whilst retaining all the advantages of CMOS technology - wide operating voltage range, very low power consumption, high input noise immunity and wide operating temperature range - these circuits have the high-speed and drive capabilities of low-power Schottky TTL (LSTTL). An extensive product range (most TTL functions and some devices from the successful HE4000B series: analog multiplexers, long time-constant multivibrators, phase-locked loops) and the aforementioned performance open new avenues in system design.

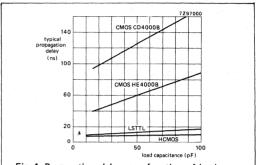

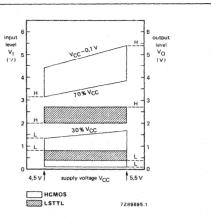

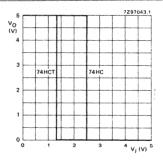

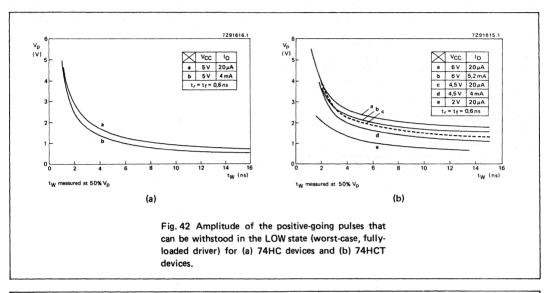

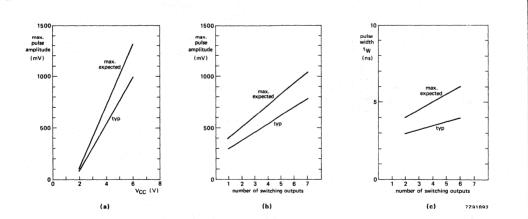

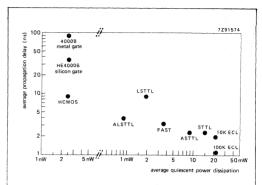

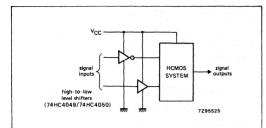

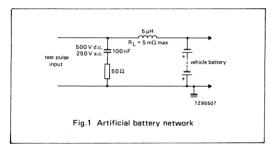

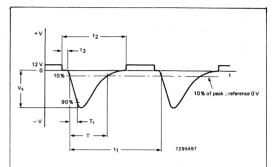

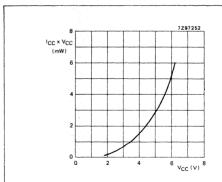

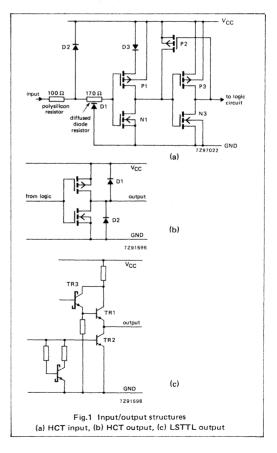

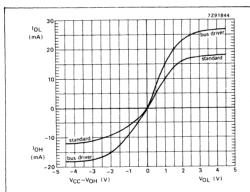

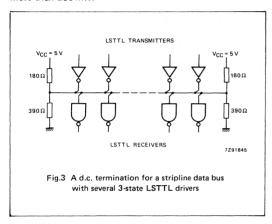

For comparison, the key performance parameters of HCMOS are shown with those of other technologies in Table 1. The propagation delay of metal-gate CMOS ruled out CMOS for many applications until the arrival of our HE4000B series. Now, our  $3\,\mu\mathrm{m}$  gate HCMOS technology has a speed comparable to LSTTL while retaining the important CMOS qualities, see Fig.1.

Table 2 compares the operating characteristics of the 74HC and 74HCT IC types with those of LSTTL in more

detail. 74HC and 74HCT devices are ideal for use in new equipment designs and, as alternatives to TTL devices, in existing designs. The 74HCT circuits which are direct replacements for LSTTL circuits also enhance performance in many respects.

Fig. 1 Propagation delay as a function of load capatance;  $V_{CC}$  = 5 V,  $T_{amb}$  = 25 °C.

Table 1 Comparison of CMOS and TTL technologies; supply voltage  $V_{CC}$  = 5 V; ambient temperature  $T_{amb}$  = 25 °C; load capacitance  $C_L$  = 15 pF

|             | technology                      | нсмоѕ     | metal gate<br>CMOS | standard<br>TTL | low-power<br>Schottky<br>TTL | Schottky<br>TTL | advanced<br>low-power<br>Schottky<br>TTL | advanced<br>Schottky<br>TTL | Fairchild<br>advanced<br>Schottky<br>TTL |

|-------------|---------------------------------|-----------|--------------------|-----------------|------------------------------|-----------------|------------------------------------------|-----------------------------|------------------------------------------|

| parameter   | family                          | 74HC      | 4000<br>CD HE      | 74              | 74LS                         | 74S             | 74ALS                                    | 74AS                        | 74F                                      |

| Power diss  | sipation, typ. (mW)             |           |                    |                 |                              |                 |                                          |                             |                                          |

| Gate        | static                          | 0.0000025 | 0.001              | 10              | 2                            | 19              | 1.2                                      | 8.5                         | 5.5                                      |

| Cate        | dynamic @ 100 kHz               | 0.075     | 0.1                | 10              | 2                            | 19              | 1.2                                      | 8.5                         | 5.5                                      |

| 0           | static                          | 0.000005  | 0.001              | 300             | 100                          | 500             | 60                                       |                             | 190                                      |

| Counter     | dynamic @ 100 kHz               | 0.125     | 0.120              | 300             | 100                          | 500             | 60                                       | _                           | 190                                      |

| Propagatio  | on delay (ns)                   |           |                    |                 |                              |                 |                                          |                             | :                                        |

| Gate        | typical                         | 8         | 94 40              | 10              | 9.5                          | 3               | 4                                        | 1.5                         | 3                                        |

| Gate        | maximum                         | 14        | 190 80             | 20              | 15                           | 5               | 7                                        | 2.5                         | 4                                        |

| Delay/pov   | ver product (pJ)                |           |                    |                 |                              |                 |                                          |                             |                                          |

| Gate        | at 100 kHz                      | 0.52      | 9 4                | 100             | 19                           | 57              | 4.8                                      | 13                          | 16.5                                     |

| Maximum     | clock frequency (MHz)           |           |                    |                 | 1                            |                 |                                          |                             | -                                        |

|             | typical                         | 55        | 4 12               | 25              | 33                           | 100             | 60                                       | 160                         | 125                                      |

| D-type flip | p-flop<br>minimum               | 30        | 2 6                | 15              | 25                           | 75              | 40                                       |                             | 100                                      |

|             |                                 | 1         |                    | 15              | 25                           |                 |                                          | <del>-</del> ''- '          | 100                                      |

| Counter     | typical                         | 45        | 2 6                | 32              | 32                           | 70              | 45                                       | -                           | 125                                      |

|             | minimum                         | 25        | 1 3                | 25              | 25                           | 40              | -                                        |                             | 100                                      |

| Output dr   |                                 |           |                    | 1               |                              |                 |                                          |                             |                                          |

|             | standard outputs                | 6         | 0.51 0.8<br>1.6    | 16<br>48        | 8 24                         | 20<br>64        | 8 24                                     | 20                          | 20                                       |

|             | bus outputs                     | 0         | 1.6                | 48              | 24                           | 04              | 24                                       | 48                          | 64                                       |

| Fan-out (   |                                 | 10        | 1 2                | 40              | 20                           | 50              | 20                                       | 50                          |                                          |

|             | standard outputs<br>bus outputs | 15        | 1 2                | 120             | 60                           | 50<br>160       | 60                                       | 50<br>120                   | 50<br>160                                |

Table 2: Comparison of HCMOS and LSTTL circuits ( $V_{CC} = 5 \text{ V}$  unless stated otherwise;  $C_L = 50 \text{ pF}$ )

| characteristic                                                                                                  | 74HCXXX (note 1)<br>74HCTXXX | 74LSXXX        |

|-----------------------------------------------------------------------------------------------------------------|------------------------------|----------------|

| Max. quiescent power dissipation over temp, range at V <sub>CCmax</sub>                                         |                              |                |

| per gate (mW)                                                                                                   | 0.027                        | 6              |

| per flip-flop (mW)                                                                                              | 0.11                         | 22             |

| per 4-stage counter (mW)                                                                                        | 0.44                         | 175            |

| per transceiver/buffer (mW)                                                                                     | 0.055                        | 60             |

| Max. dynamic power dissipation (C <sub>1</sub> = 50 pF)                                                         |                              |                |

| at f <sub>i</sub> (MHz) 0.1                                                                                     | 1 10                         | 0.1 to 1 10    |

| per gate (mW) 0.25                                                                                              | 2.25 22                      | 6 22           |

| per flip-flop (mW) 0.35                                                                                         | 2.5 24                       | 22 27          |

| per 4-stage counter (mW) 0.70                                                                                   | 3 27                         | 175 200        |

| per buffer/transceiver (mW) 0.30                                                                                | 2.5 24                       | 60 90          |

| Operating supply voltage (V)                                                                                    | 2 to 6 (HC)                  | 4.75 to 5.25   |

|                                                                                                                 | 4.5 to 5.5 (HCT)             |                |

| Operating temperature range (°C)                                                                                | -40 to +85                   | 0 to +70       |

|                                                                                                                 | -40 to +125                  |                |

| Max. noise margin ( $V_{NMH}/V_{NML}V$ ; $I_{OHCMOS} = 20 \mu A$ ; $I_{OLSTTL} = 4 mA$ )                        | 1.4/1.4 (HC)                 | 0.7/0.4        |

|                                                                                                                 | 2.9/0.7 (HCT)                |                |

| Input switching voltage stability over temp, range                                                              | ±60 mV                       | ±200 mV        |

| Min. output drive current at Tamb max and VCCmin (mA)                                                           |                              |                |

| source current (V <sub>OH</sub> = 2.7 V; note 2)                                                                |                              |                |

| standard logic                                                                                                  | <b>–8</b>                    | -0.4           |

| bus logic                                                                                                       | <b>–12</b>                   | -2.6           |

| sink current                                                                                                    |                              |                |

| standard logic (V <sub>OL</sub> = 0.4 V)                                                                        | 4                            | 4              |

| standard logic (V <sub>OL</sub> = 0.5 V)                                                                        | 6                            | 8              |

| bus logic $(V_{OL} = 0.4 \text{ V})$                                                                            | 8                            | 12             |

| bus logic ( $V_{OL} = 0.5 \text{ V}$ )                                                                          | 9                            | 24             |

| Typ. output transition time (ns) $(C_L = 15 pF)$                                                                |                              |                |

| standard logic                                                                                                  |                              |                |

| t <sub>TLH</sub>                                                                                                | 6                            | 15             |

| <sup>t</sup> THL                                                                                                | 6                            | 6              |

| bus logic                                                                                                       |                              |                |

| <sup>t</sup> TLH                                                                                                | 4                            | 15             |

| <sup>t</sup> THL                                                                                                | 4                            | 6              |

| Typ. propagation delay (ns) ( $C_L = 15 \text{ pF}$ ; note 3)                                                   |                              |                |

| gate tPHL/tPLH                                                                                                  | 8/8                          | 8/11           |

| flip-flop t <sub>PLH</sub>                                                                                      | 14                           | 15             |

| t <sub>PHL</sub>                                                                                                | 14                           | 22             |

| Typ. clock rate of a flip-flop; note 5 (MHz)                                                                    | 50                           | 33             |

| Max. input current (μA)                                                                                         |                              |                |

| grafiga (filozofia) de la companya (filozofia) de la companya (filozofia) de la companya (filozofia) de la comp | -1                           | -400 to -800   |

| i Jin da da karangan da ka  | 1                            | 40             |

| 3-state output leakage current ( $\pm \mu A$ )                                                                  | 5                            | 20             |

| Reliability (%/1000 h at 60% confidence level)                                                                  | 0.0005                       | 0.008 (note 4) |

#### Notes

- 1. Data valid for HCMOS between -40 °C and +85 °C.

- 2.  $V_{\mbox{OH}}$  for a few LSTTL bus outputs is specified as 2.4 V.

- 3. Refer to data sheets for the effect of capacitive loading.

- 4. RADC report.

- 5. Measured with a 50% duty factor for HCMOS. For LSTTL, per industry convention, the maximum clock frequency is specified with no constraints on rise and fall times, pulse width or duty factor.

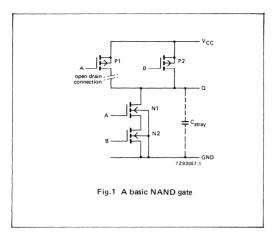

#### CONSTRUCTION

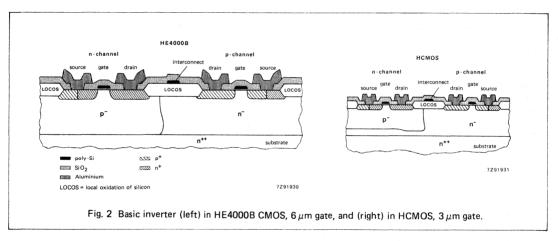

Our HCMOS family is a result of a continuing development programme to enhance the proven polysilicon-gate CMOS process. Figure 2 shows the construction of a basic inverter from the HE4000B series and its HCMOS successor.

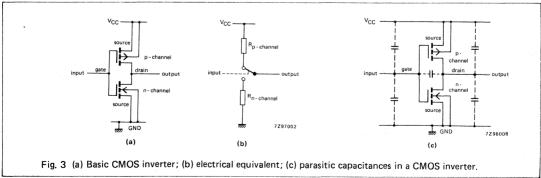

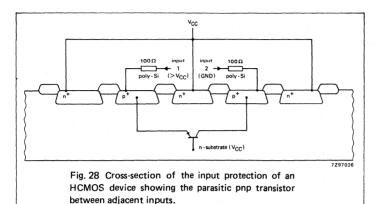

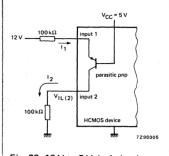

The polysilicon gate of a HCMOS transistor is deposited over a thin gate oxide before the source and drain diffusions are defined. Source and drain regions are formed using ion implantation, with the polysilicon gates acting as masks for the implantation. The source and drain are automatically aligned to the gate, minimizing gate-to-source and gate-to-drain capacitances. In addition, the junction capacitances, which are proportional to the junction area, are reduced because of the shallower diffusions. Figure 3(c) shows the parasitic capacitances in a CMOS inverter.

In a metal-gate CMOS transistor, the source and drain are formed before the gate is deposited. Moreover, the metal gate must overlap the source and drain to allow for alignment tolerances. This is why a metal-gate CMOS

transistor has a higher overlap capacitance than an HCMOS transistor. Furthermore, the deeper diffusions of metal-gate CMOS make the junction capacitance larger.

In a silicon-gate MOS transistor, there are three interconnect layers (diffusion, polysilicon and metal) instead of the two layers (diffusion and metal) in a metal-gate MOS transistor. This makes a silicon-gate MOS transistor more compact. The shorter gate length means higher drive capability, which in turn increases the speed at which a silicon-gate MOS transistor can charge or discharge junction capacitance. The drain current of a saturated MOS transistor which determines the speed of the transistor is:

$$I_{DS} = \frac{-\beta}{2} \times \frac{\text{gate width}}{\text{gate length}} \times (\text{gate voltage - threshold voltage})^2$$

where  $\boldsymbol{\beta}$  is the current gain factor which is proportional to the thickness of the oxide layer.

The threshold voltage is typically 0.7 V for HCMOS.

#### AC CHARACTERISTICS

#### Test conditions

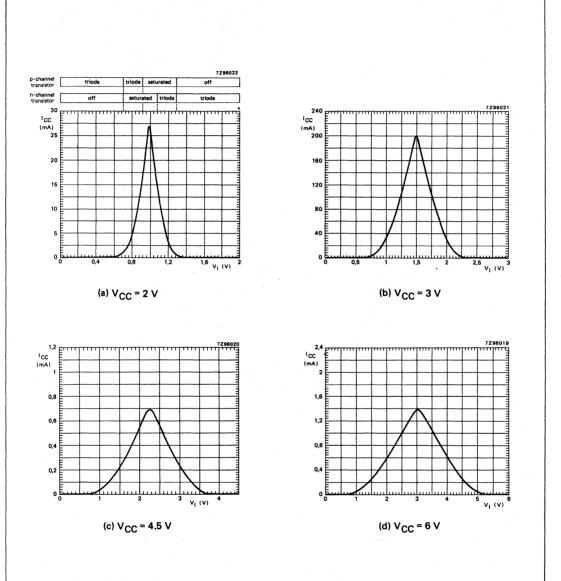

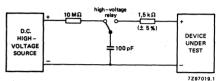

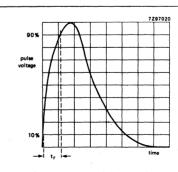

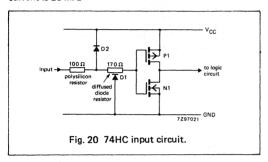

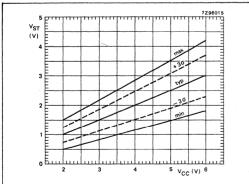

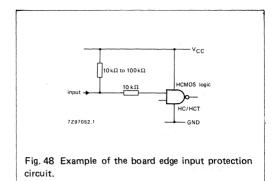

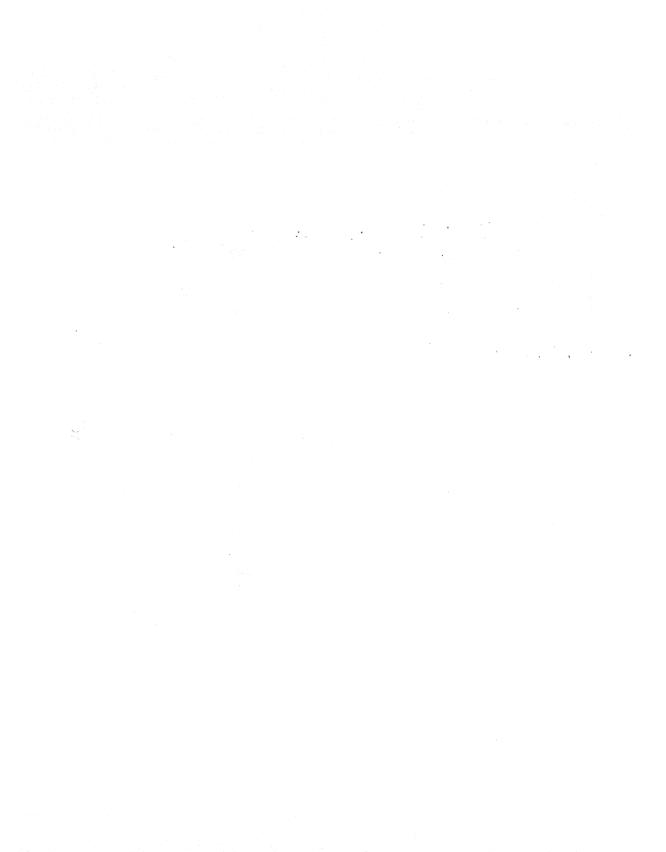

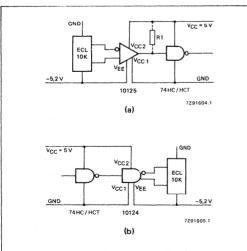

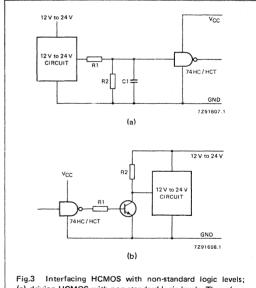

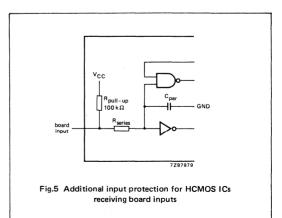

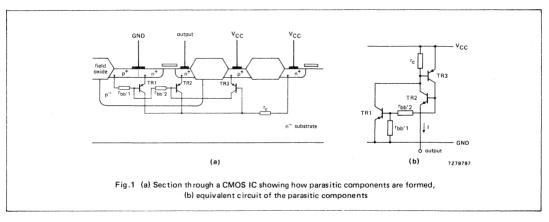

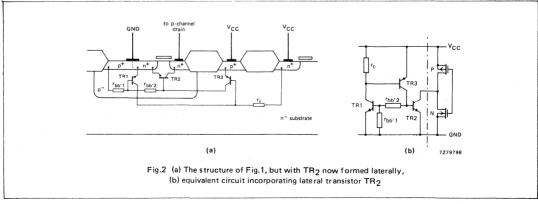

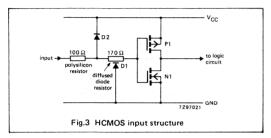

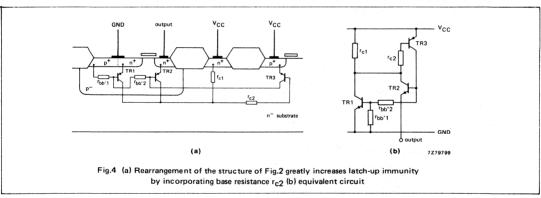

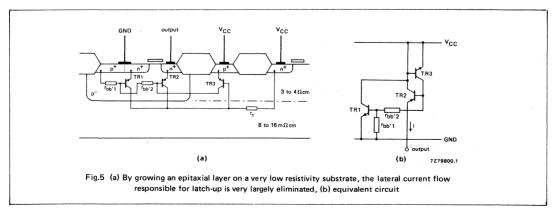

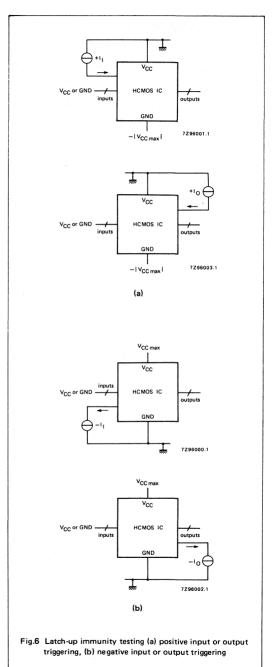

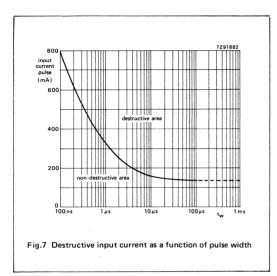

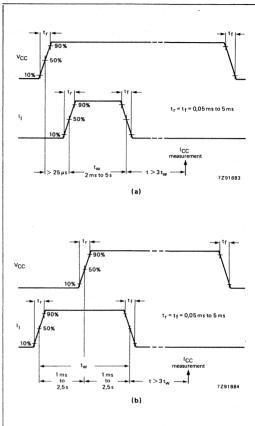

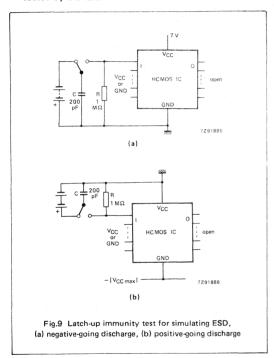

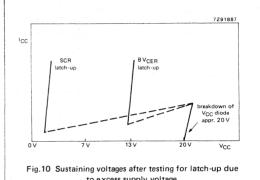

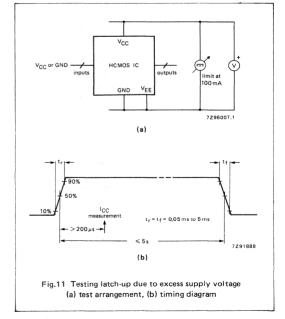

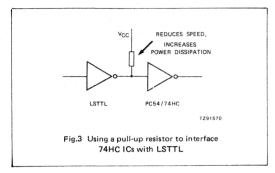

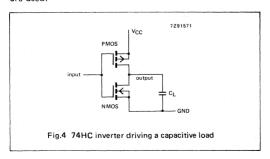

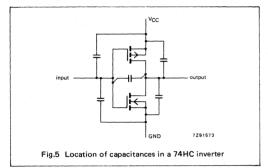

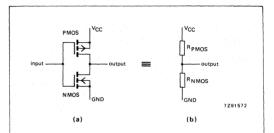

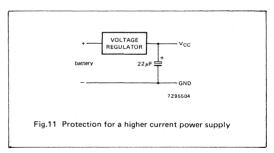

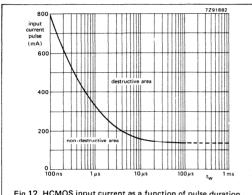

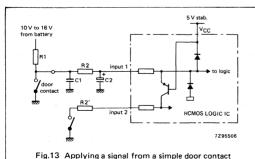

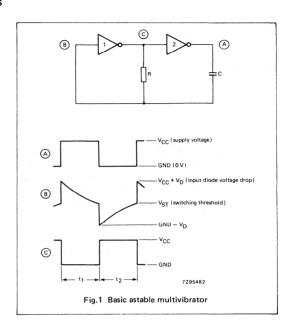

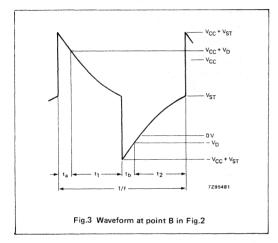

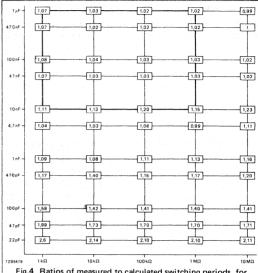

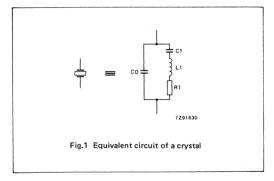

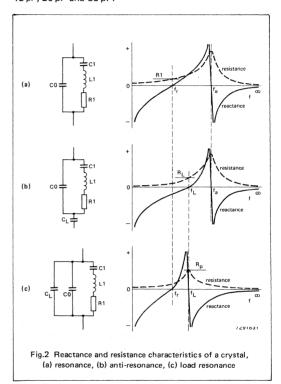

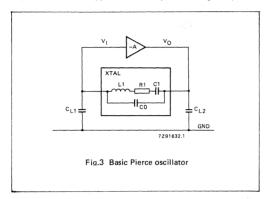

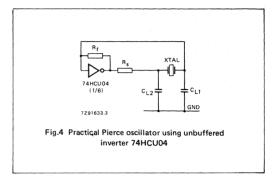

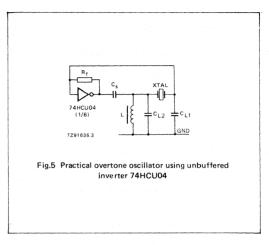

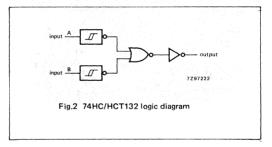

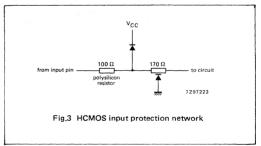

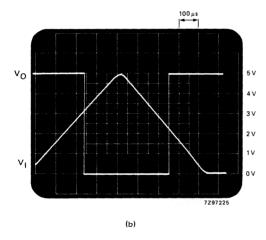

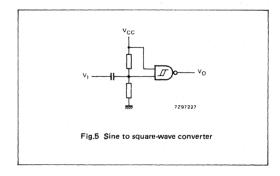

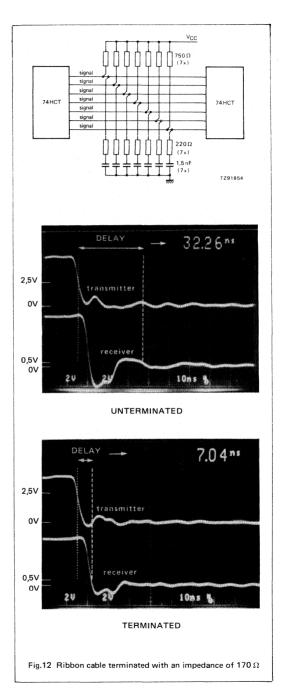

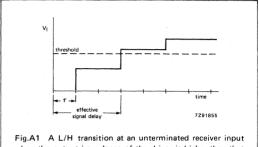

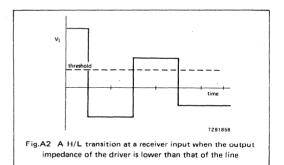

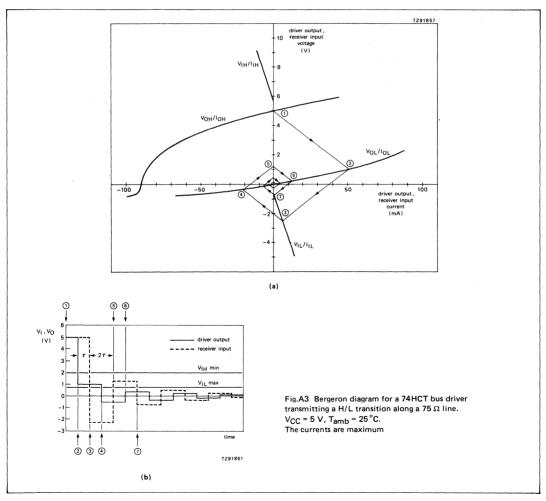

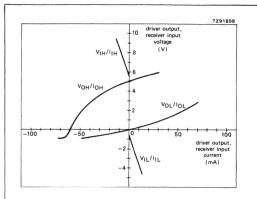

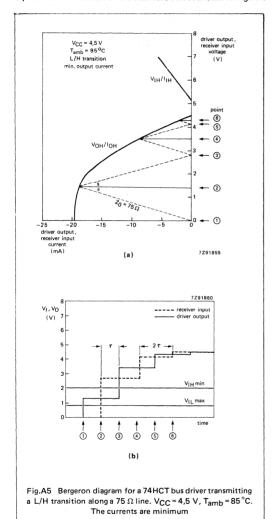

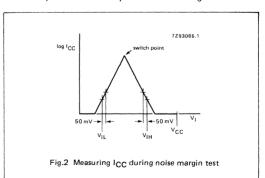

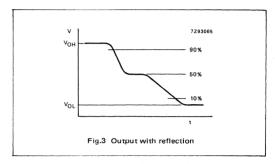

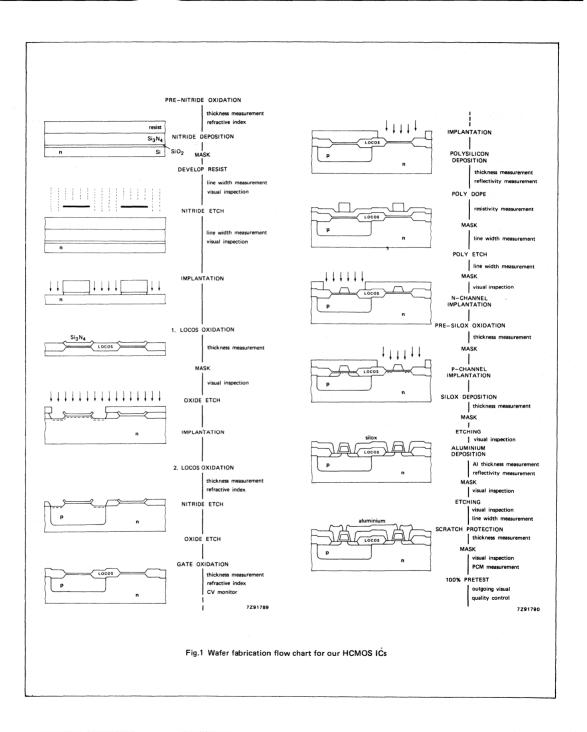

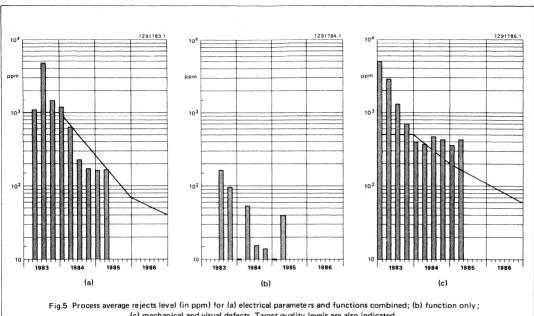

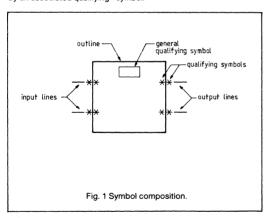

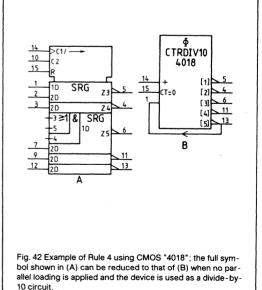

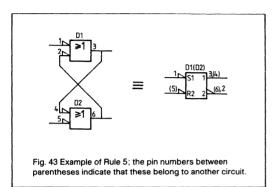

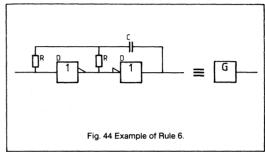

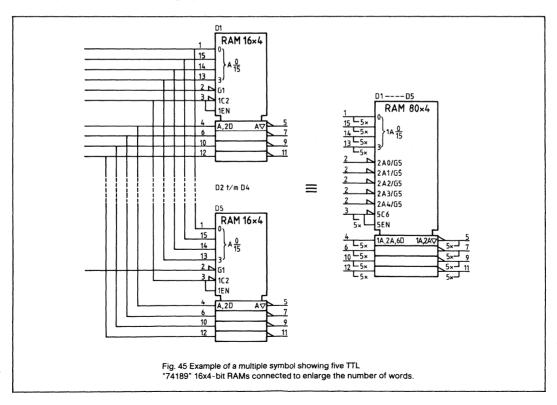

The propagation delays and transition times specified in the HCMOS data sheets are guaranteed when the circuits are tested according to the conditions stated in the chapter 'Family Characteristics', section 'Family Specifications'. For some circuits such as counters and flip-flops, the test conditions are defined further by the a.c. set-up requirements specified in the data sheet.